全国咨询热线:400-998-9522

类别:行业资讯 发布时间:2020-08-20 浏览人次:

武汉新芯研发成功的三片晶圆堆叠技术备受关注。有人说,该技术在国际上都处于先进水平,还有人说能够“延续”摩尔定律。既然3D芯片堆叠技术有如此大的作用,那今天芯师爷就跟大家一起揭开它的面纱。

日前,武汉新芯对外宣布称,基于其三维集成技术平台的三片晶圆堆叠技术研发成功。该消息一出就有业内人士表示,随着这一技术的突破,武汉新芯3D芯片堆叠技术居于国际先进、国内领先的水平。

还有业内人士指出,3D芯片堆叠是新的技术,可将存储、逻辑、传感器于一体,能够缩小尺寸且提供性能,是朝摩尔定律的方向迈进了一步。那么问题来了,3D芯片堆叠技术到底是什么?

3D芯片堆叠技术发展历程

上世纪九十年代,BGA封装(球栅阵列封装)替代了外引脚封装,焊料球凸点面阵使封装尺寸减小,输入和输出端口数量增加,功能和性能增加。然而随着封装技术的发展,在平面方向上的封装已经达到了极限。

另一方面,随着CMOS工艺的不断发展,继续等比例缩小的局限越发明显,系统设计师们开始越来越多地转向芯片封装,而不是继续依赖在单一芯片上集成更多的器件来提高性能。

在传统的集成电路技术中,作为互连层的多层金属位于2D有源电路上方,互连的基本挑战是全局互连的延迟,特别随着等比例缩小的持续进行,器件密度不断增加,延迟问题就更为突出。

为了避免这种延迟,同时也为了满足性能、频宽和功耗的要求,设计人员开发出在垂直方向上将芯片叠层的新技术,也就是三维堆叠封装技术,该技术可以穿过有源电路直接实现高效互连。

另外一些组织和公司也都在积极开发基于TSV(硅通孔,through silicon via)的3D芯片技术。究其原因,是因为许多芯片厂商都担心将来继续缩减制程尺寸时,所花费的成本难以承受,甚至不久的将来可能会被迫停止芯片制程缩减方面的开发。

随着硅片减薄技术的成功使用,多芯片堆叠封装的厚度几乎与过去BGA封装具有相同的厚度(约1.2毫米)。因此,3D芯片堆叠技术在缩小芯片尺寸的同时,还能有效地增强电子产品的功能和性能。

3D芯片堆叠技术简介

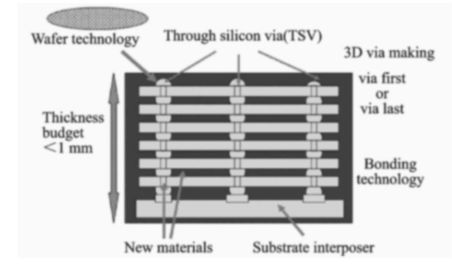

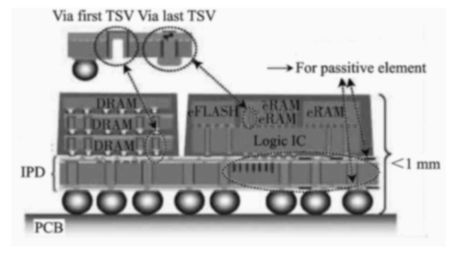

与传统的二维芯片把所有的模块放在平面层相比,三维芯片允许多层堆叠,而过TSV用来提供多个晶片垂直方向的通信。其中,TSV是3D芯片堆叠技术的关键。

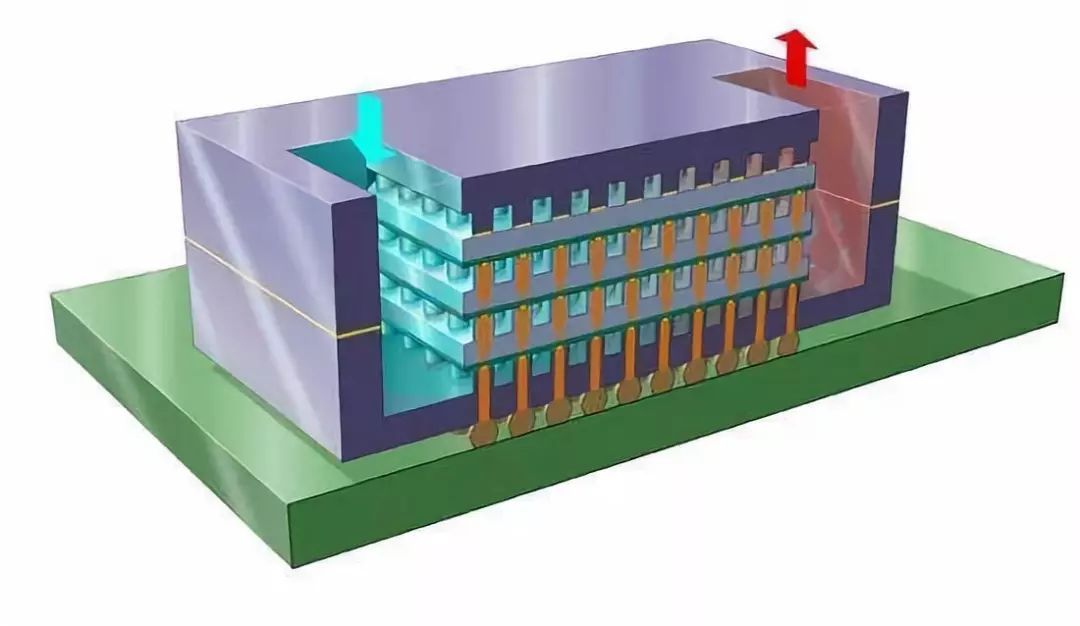

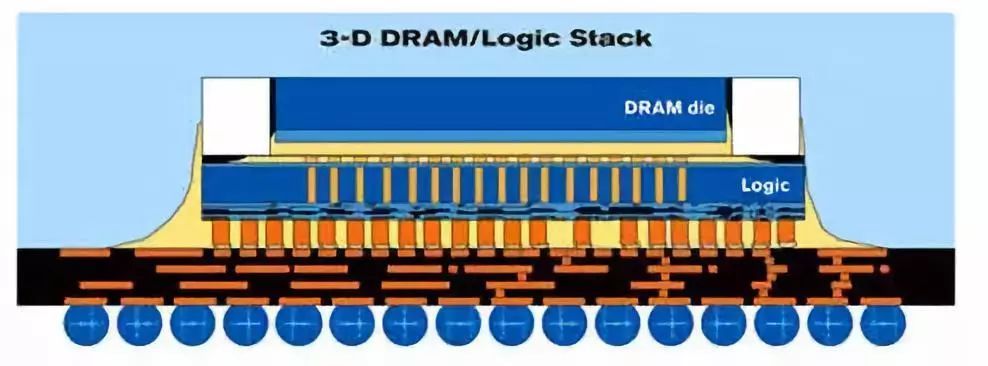

3D芯片堆叠结构示意图

3D堆叠技术是把不同功能的芯片或结构,通过堆叠技术或过孔互连等微机械加工技术,使其在Z轴方向上形成立体集成、信号连通及圆片级、芯片级、硅帽封装等封装和可靠性技术为目标的三维立体堆叠加工技术。该技术用于微系统集成,是继片上系统(SOC)、多芯片模块(MCM)之后发展起来的系统级封装的先进制造技术。

3D芯片技术的类别

从SiP系统级封装的传统意义上来讲,凡是有芯片堆叠的都可以称之为3D,因为在Z轴上有了功能和信号的延伸,无论此堆叠是位于IC内部还是IC外部。但是,随着技术的发展,3D芯片技术却有了其更新、更独特的含义。

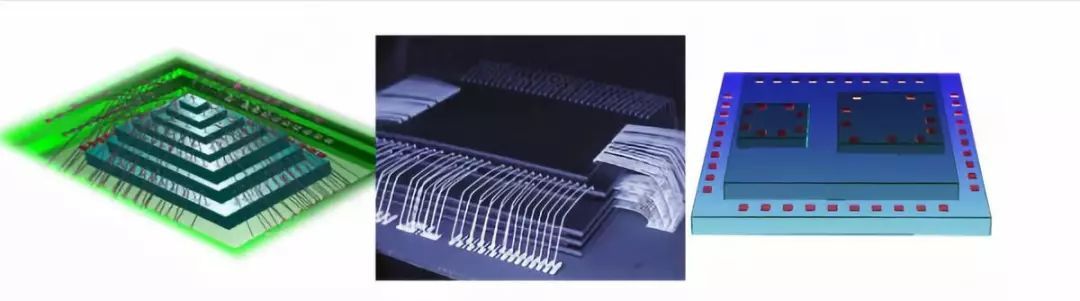

1.基于芯片堆叠式的3D技术

3D IC的初期型态,目前仍广泛应用于SiP领域,是将功能相同的裸芯片从下至上堆在一起,形成3D堆叠,再由两侧的键合线连接,最后以系统级封装(System-in-Package,SiP)的外观呈现。堆叠的方式可为金字塔形、悬臂形、并排堆叠等多种方式,参看下图。

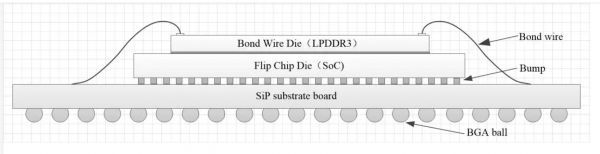

另一种常见的方式是将一颗倒装焊(flip-chip)裸芯片安装在SiP基板上,另外一颗裸芯片以键合的方式安装在其上方,如下图所示,这种3D解决方案在手机中比较常用。

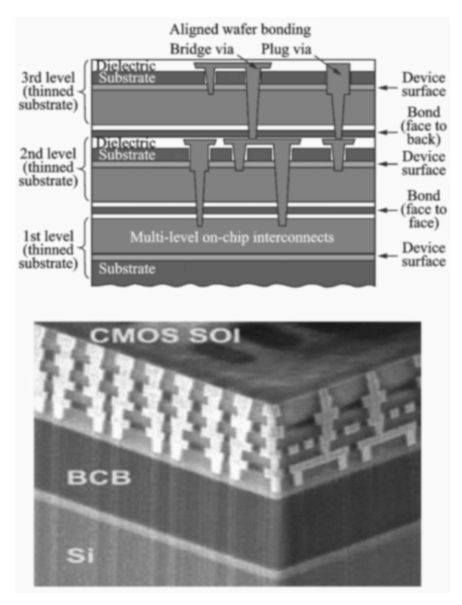

2.基于有源TSV的3D技术

在这种3D集成技术中,至少有一颗裸芯片与另一颗裸芯片叠放在一起,下方的那颗裸芯片是采用TSV技术,通过TSV让上方的裸芯片与下方裸芯片、SiP基板通讯。如下图所示:

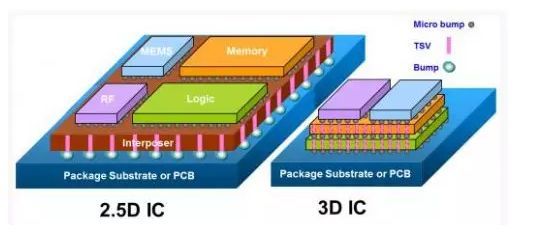

下图显示了无源TSV和有源TSV分别对应的2.5D和3D技术。

以上的技术都是指在芯片工艺制作完成后,再进行堆叠形成3D,其实并不能称为真正的3D IC 技术。这些手段基本都是在封装阶段进行,我们可以称之为3D集成、3D封装或者3D SiP技术。

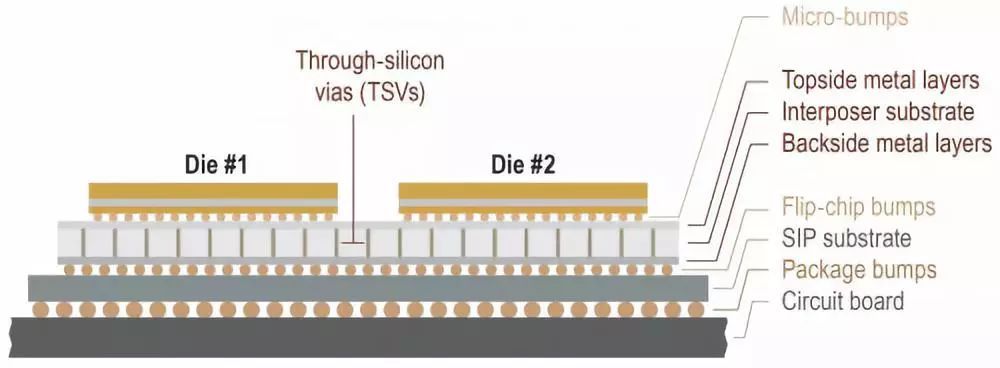

3.基于无源TSV的3D技术

在SiP基板与裸芯片之间放置一个中介层(interposer)硅基板,中介层具备硅通孔(TSV),通过TSV连结硅基板上方与下方表面的金属层。有人将这种技术称为2.5D,因为作为中介层的硅基板是无源被动元件,TSV硅通孔并没有打在芯片本身上。如下图所示:

4.基于芯片制造的3D技术

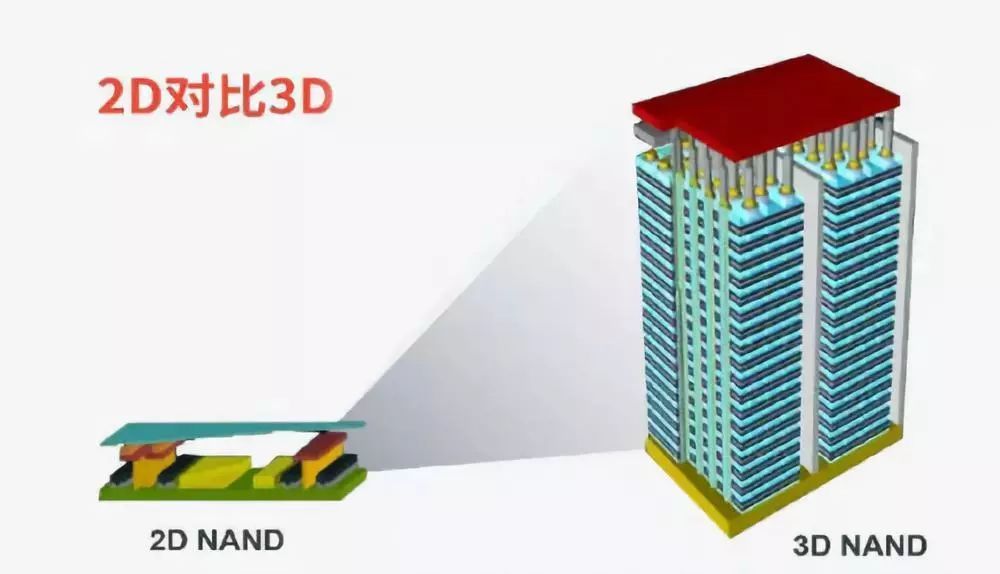

目前,基于芯片制造的3D技术主要应用于3D NAND FLASH上。东芝和三星在 3D NAND 上的开拓性工作带来了两大主要的 3D NAND 技术。

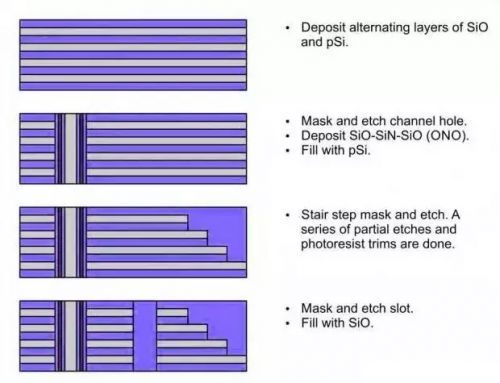

东芝开发了 Bit Cost Scalable(BiCS)的工艺。BiCS 工艺采用了一种先栅极方法(gate-first approach),这是通过交替沉积氧化物(SiO)层和多晶硅(pSi)层实现的。然后在这个层堆叠中形成一个通道孔,并填充氧化物-氮化物-氧化物(ONO)和 pSi。然后沉积光刻胶,通过一个连续的蚀刻流程,光刻胶修整并蚀刻出一个阶梯,形成互连。最后再蚀刻出一个槽并填充氧化物。如下图所示:

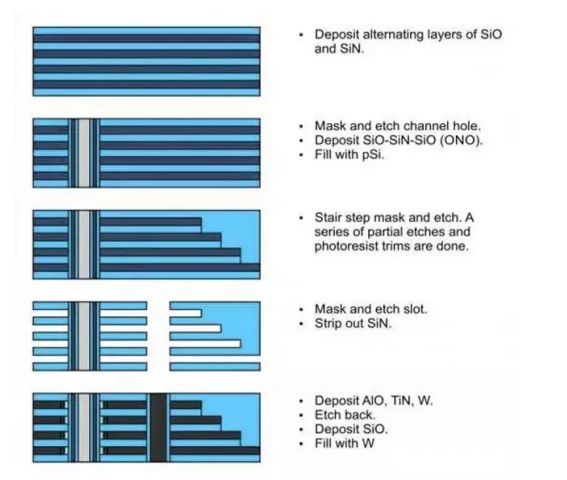

三星则开发了 Terabit Cell Array Transistor (TCAT)工艺。TCAT 是一种后栅极方法( gate-last approach),其沉积的是交替的氧化物和氮化物层。然后形成一个穿过这些层的通道并填充 ONO 和 pSi。然后与 BiCS 工艺类似形成阶梯。最后,蚀刻一个穿过这些层的槽并去除其中的氮化物,然后沉积氧化铝(AlO)、氮化钛(TiN)和钨(W)又对其进行回蚀(etch back),最后用坞填充这个槽。如下图所示:

3D NAND目前已经能做到64层甚至更高,其产量正在超越 2D NAND,而且随着层数的进一步扩展,3D NAND还能继续将摩尔定律很好地延续。

TSV——层间互连技术

上文提到,在3D芯片堆叠技术当中,TSV是其关键,那TSV到底又是什么呢?

TSV(through silicon via),中文为硅通孔。TSV通过再芯片与芯片之间、晶圆与晶圆之间制作垂直导通,实现芯片之间互连,能够使三维方向堆叠的密度最大,外形尺寸最小,并且大大改善芯片速度和降低功耗。

采用TSV技术堆叠的器件

TSV与目前应用于多层互连的通孔有所不同。一方面,TSV通孔的直径通常仅为1-100Lm(光通量的物理单位),深度10-400Lm,为集成电路或其他多功能器件高密度混合集成提供可能;另一方面,它们不仅需要穿透组成叠层电路的各种材料,还需要穿透很厚的硅衬底,因此对通孔的刻蚀机技术具有较高的要求。

3D TSV互连概念模型

上图是一个3D TSV互连的概念模型,TSV是利用垂直硅通孔完成芯片互连的方法,由于连接距离更短、强度更高,它能实现更薄更小而性能更好、密度更高、尺寸和重量明显减小的封装。同时还能用于异种芯片之间的互连。

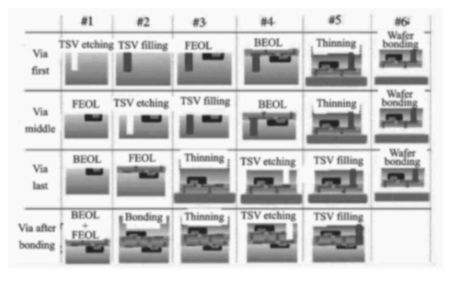

根据通孔制作的时间不同,3D TSV通孔集成方式可以分为四类:

1.先通孔工艺,即在CMOS制程之前完成硅通孔制作。先通孔工艺中的盲孔需电镀绝缘层并填充导电材料,通过硅晶圆减薄,使盲孔开口形成与背面的连接。

2.中通孔工艺,即在CMOS制程和后段制程(BEOL)之间制作通孔。

3.后通孔工艺,即在BEOL完成之后再制作通孔,由于先进行芯片减薄,通孔制成后即可与电路相连。

4.键合后通工艺,即在硅片减薄、划片之后再制作TSV。

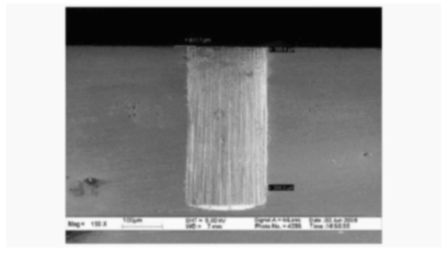

圆片上通孔制造是TSV技术的核心,目前,钻蚀TSV技术主要有两种,一种是干法刻蚀或称博世刻蚀,另一种是激光刻蚀。博世工艺为MEMS工艺而开发,快速地在去除硅的SF6等离子刻蚀和实现侧壁钝化的C4F8等离子沉积步骤之间循环切换。下图为南京电子器件所(NEDI)利用博世工艺制作的TSV硅通孔。

NEDI研制的3D TSV通孔

激光技术作为一种不需掩膜的工艺,避免了光刻胶涂布、布刻曝光、显影和去胶等工艺步骤,三星在存储器叠层中采用了这一技术。激光加工系统供应商Xsil公司(爱尔兰)为TSV带来了另一种解决方案,Xsil称激光钻孔工艺首先应用到低密度闪存及CMOS传感器中,随着工艺及生产能力的提高,将会应用到DRAM中。

TSV被许多半导体厂和研究机构认为是最有前途的封装方法,世界上50%以上的厂商都参与3D TSV互连相关方面的研究。其中,以三星,SK海力士等为首的企业在积极推广可将3D TSV的计划。此外,英特尔、台积电、格芯、高通、安森美、惠普、IBM、联电、纽约州立大学等都有在研究3D芯片堆叠技术。

3D芯片堆叠技术应用及行业影响

如今,3D芯片堆叠技术在一些设备中已经有总领性的作用。从第一代开始,Apple Watch就是由最先进的3D堆叠式芯片封装之一驱动。在该智能手表中,30种不同的芯片密封在一个塑料包层里面。为了节省空间,存储芯片堆叠在逻辑电路上面。如果没有采用芯片堆叠技术,该手表的设计就无法做到如此紧凑。

英伟达硬件工程高级副总裁布莱恩·凯莱赫表示,公司针对AI打造的Volta微处理器的运作也运用了3D堆叠技术。通过直接在GPU上面堆叠八层的高频宽存储器,这些芯片在处理效率上创造了新的记录。“我们在电力上是受限的,我们能够从存储系统腾出的任何电力,都可以用在计算上。”凯莱赫如是说。

芯片堆叠也带来了一些全新的功能。有的手机摄像头将图像传感器直接叠加在处理图像的芯片上面,额外的速度意味着它们能够对照片进行多次曝光,并将其融合在一起,在昏暗的场景里捕捉到更多的光线。

由此可见,3D芯片堆叠技术的应用市场非常大,一旦全面投入市场,将极大的提升计算机芯片性能。可以说,3D芯片堆叠技术是一个趋势和必然,日后会越来越普通。

结语:

半导体业晶圆制程即将达到瓶颈,也就代表摩尔定律可能将失效。在晶圆制程无法继续微缩下,封测业将暂时以系统级封装等技术将芯片做有效整合,提高芯片制造利润,挑起超越摩尔定律的角色。

中国台湾半导体协会理事长卢超群指出,未来半导体将要做3D垂直堆叠,全球半导体产业未来会朝向类摩尔定律成长。封测业人士指出,目前不论是在逻辑芯片上抑或是NAND Flash上,都需要3D堆叠技术,才能让芯片效益发挥最大化,也才能达到轻薄短小的程度。从这一点上看,武汉新芯基于其三维集成技术平台的三片晶圆堆叠技术研发成功,确实代表了芯片未来方向。

本文来源于网络,如有侵权,请联系我删除。

如果大家对芯片堆叠系统有任何焊接疑问,我们可以提供专业的技术支持和服务。新品开发可以到我们公司进行新产品的芯片堆叠,我们中科同志科技的3D芯片堆叠系统、芯片堆叠系统、高真空炉已为多家公司解决了3D封装的问题。www.torch.cc

刷屏的3D芯片堆叠技术,到底是什么?...

2020-08-20华为鸿蒙系统发布...

2020-08-19研发成功!三维芯片堆叠技术取得重大突破_TORCH赵永先_新浪博客,TORCH赵永先,...

2020-08-19MiniLED芯片焊盘表面结构对封装的影响分析...

2020-08-18鸿蒙发布余承东:美国压力令华为更有战斗力...

2020-08-18千万别忘记!8月15日是日本投降纪念日...

2020-08-15